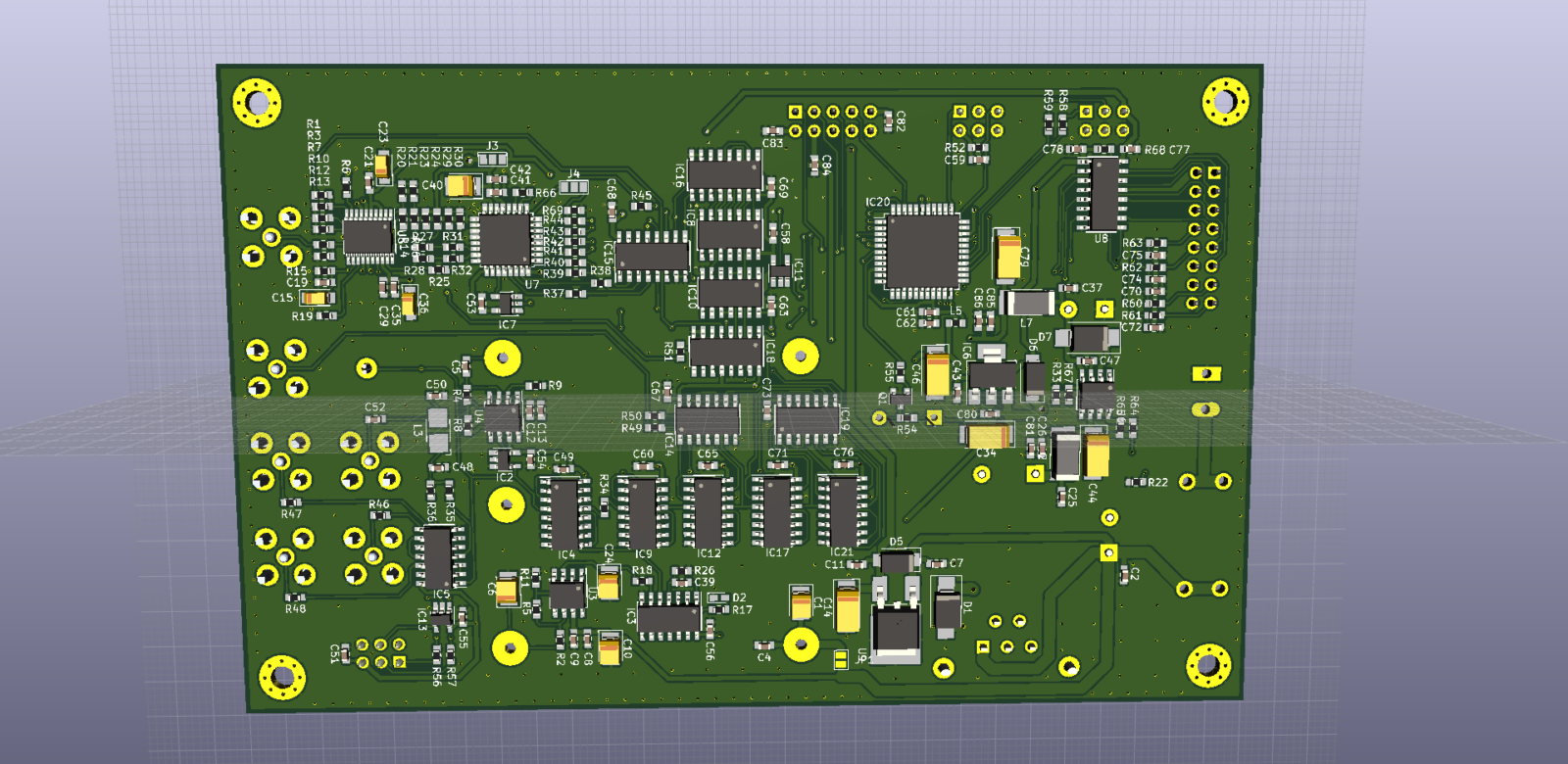

Při konstrukci čítače FC-1300 jsme zcela přešli od návrhového programu Eagle Cadsoft k open-source návrhovému systému KiCad EDA. Nutno podotknout, že KiCad je nástrojem nejen srovnatelným, ale dle našeho názoru výrazně lepším než zmíněný Eagle. Jeho “nulová” pořizovací cena je už jen bonbonkem na dortu. Nulová píšu v úvozovkách proto, neboť je třeba se s programem naučit a investovat tak svůj čas. Výsledek ale vážně stojí za to.

V KiCadu vše funguje spolehlivě, stojí za ním velká komunita vývojářů. Má řadu pokročilých funkcí. Velmi užitečný je například adaptivní routing, kdy při tažení cesty na desce plošných spojů mohou ostatní cesty nebo prokovy “uhýbat” nově vedené cestě.

Stojí rovněž za zmíňku, že KiCad je hojně používán a vlastně vzešel z prostředí evropské organizace pro jaderný výzkum – CERN

3D simulace výsledné desky:

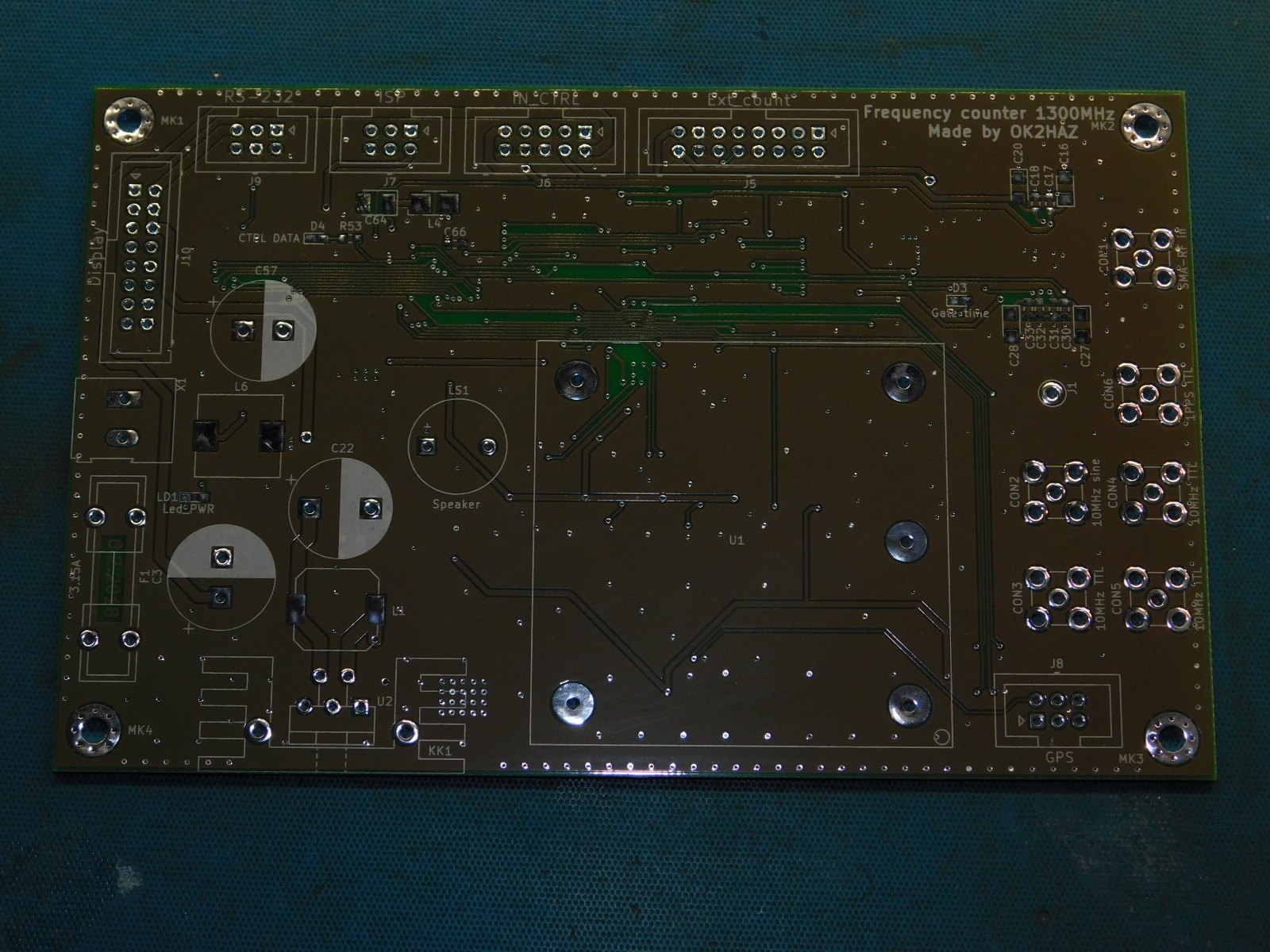

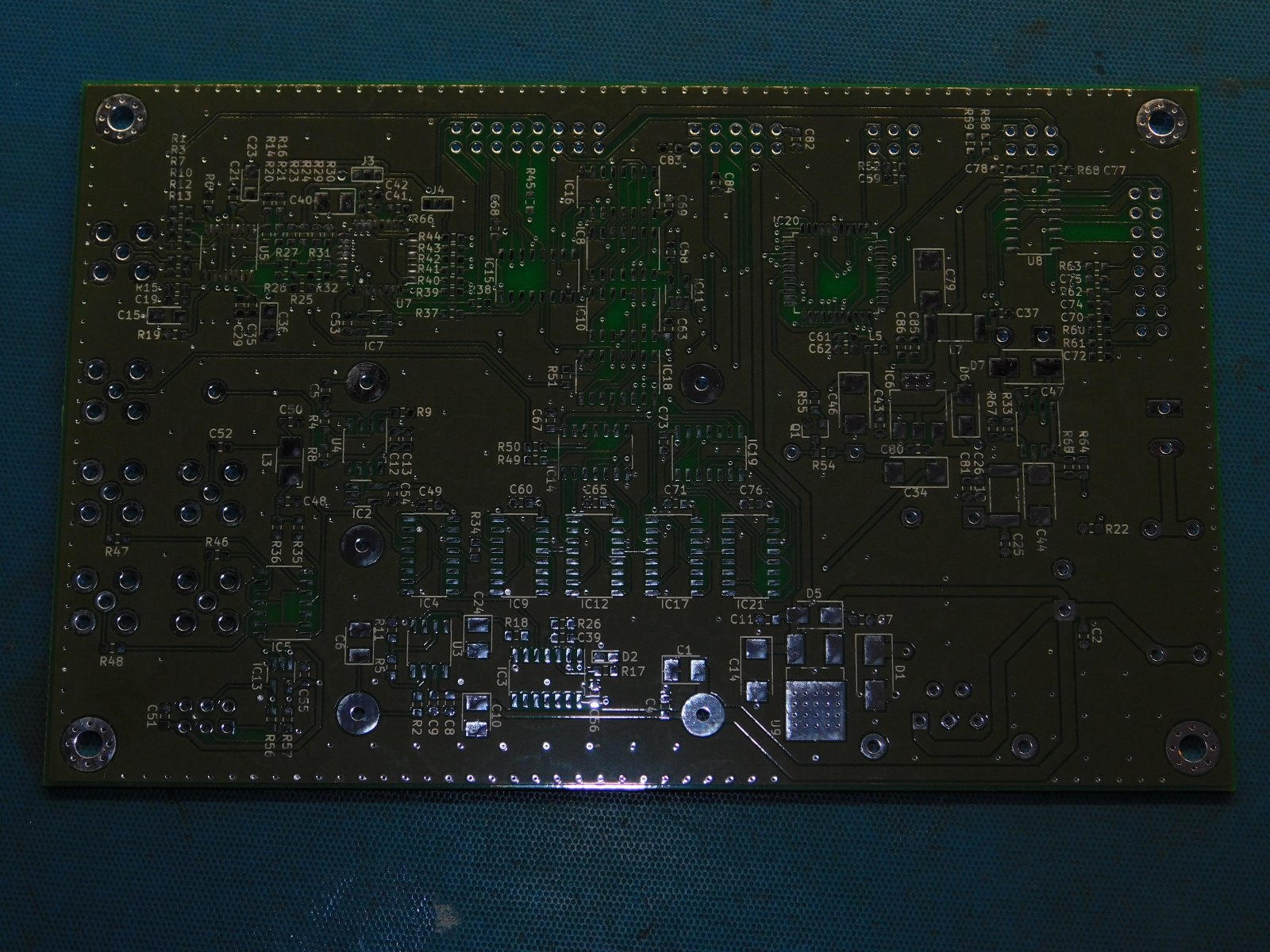

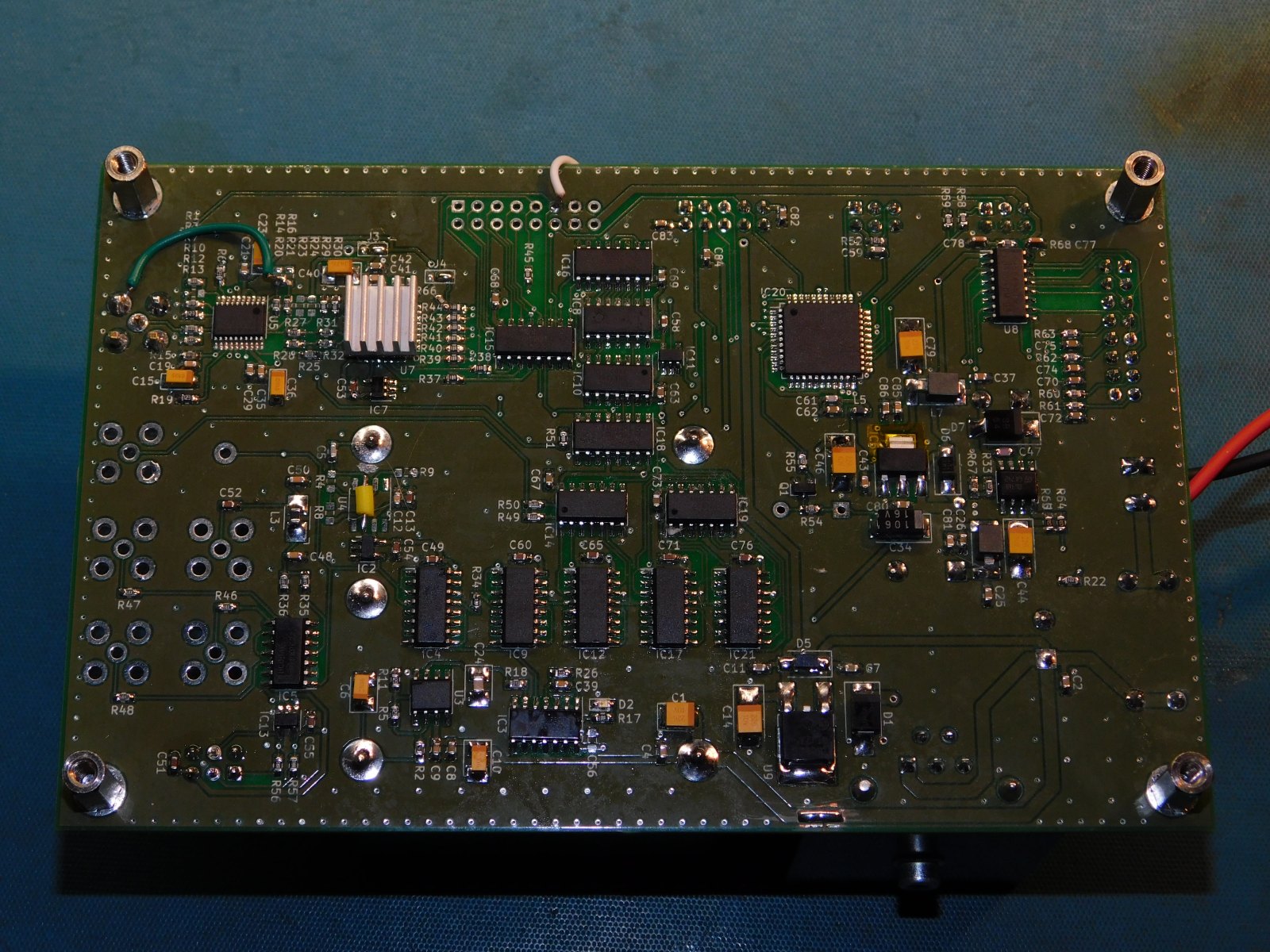

Navrženou prototypovou desku jsem nechal vyrobit v PragoBoard (kusová cena v pool servisu 1200,-kč za 1ks), desky další necháme vyrobit v čínském Allpcb.

Modul desky čítače je navržen pro vstupní napětí 12V, tímto napětím je přímo napájen OCXO, externí periferie na vstupním modulu, silový DC-DC měnič U2 s LM2596.

Zbytek desky pak pracuje na napěťových úrovních:

+5VA – pro analogové vstupní OZ a děličku, z 12V pomocí lineárního stabilizátoru U9 LM7805

-5VA – pro analogové vstupní OZ, z +5VD větve pomocí DC-DC měniče MC34063

+5VD – pro silové napájení LED displeje U2 – LM2596

+3,3V – pro zbytek logiky a CPU, z +5VD pomocí AMS1117-3,3

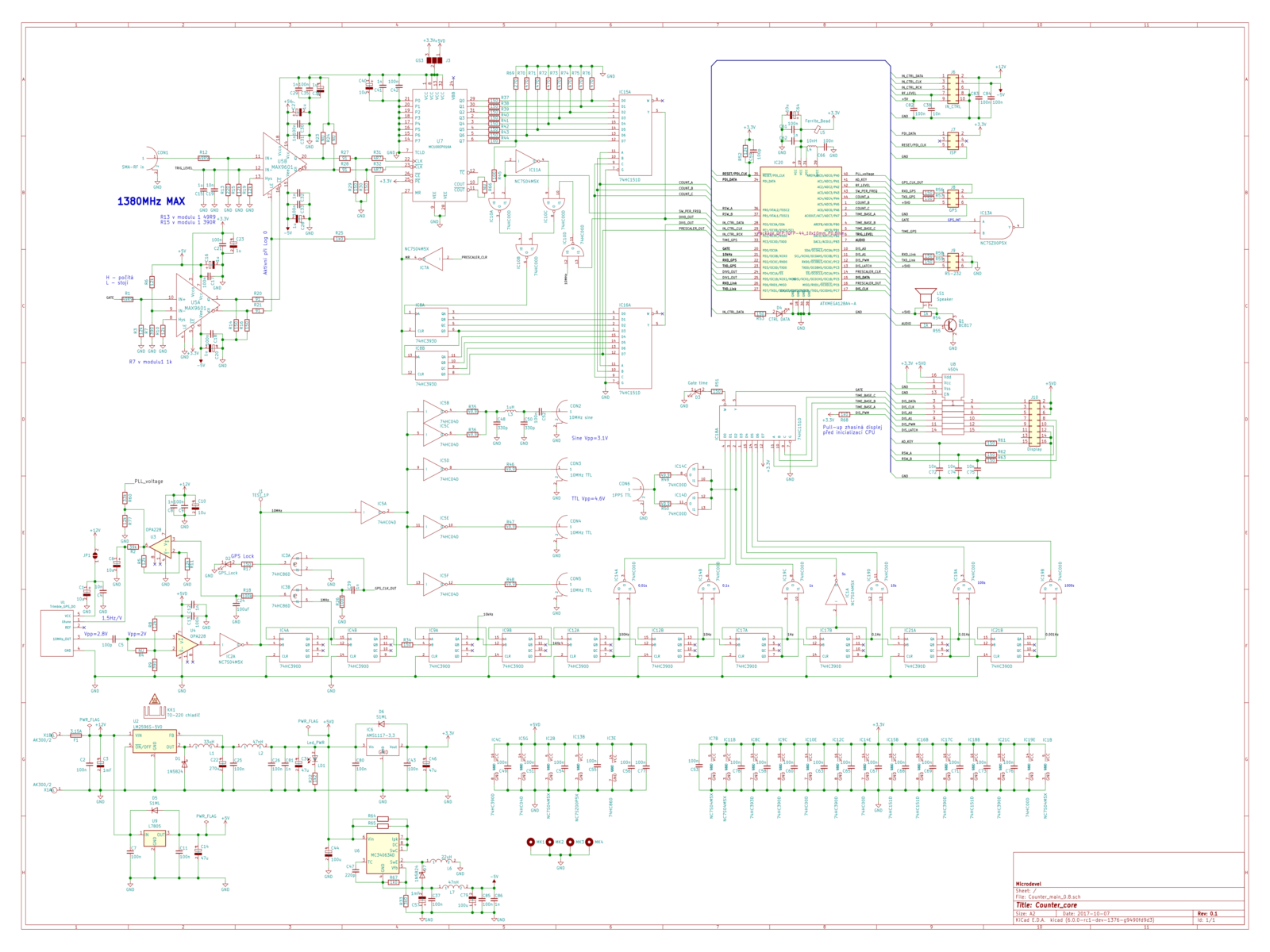

Schéma:

Vstupní obvody:

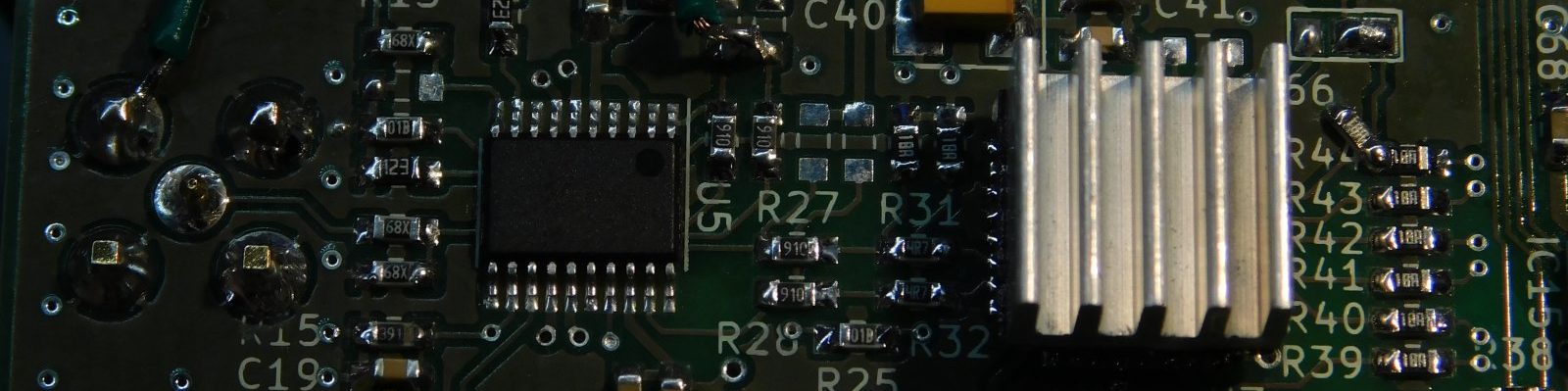

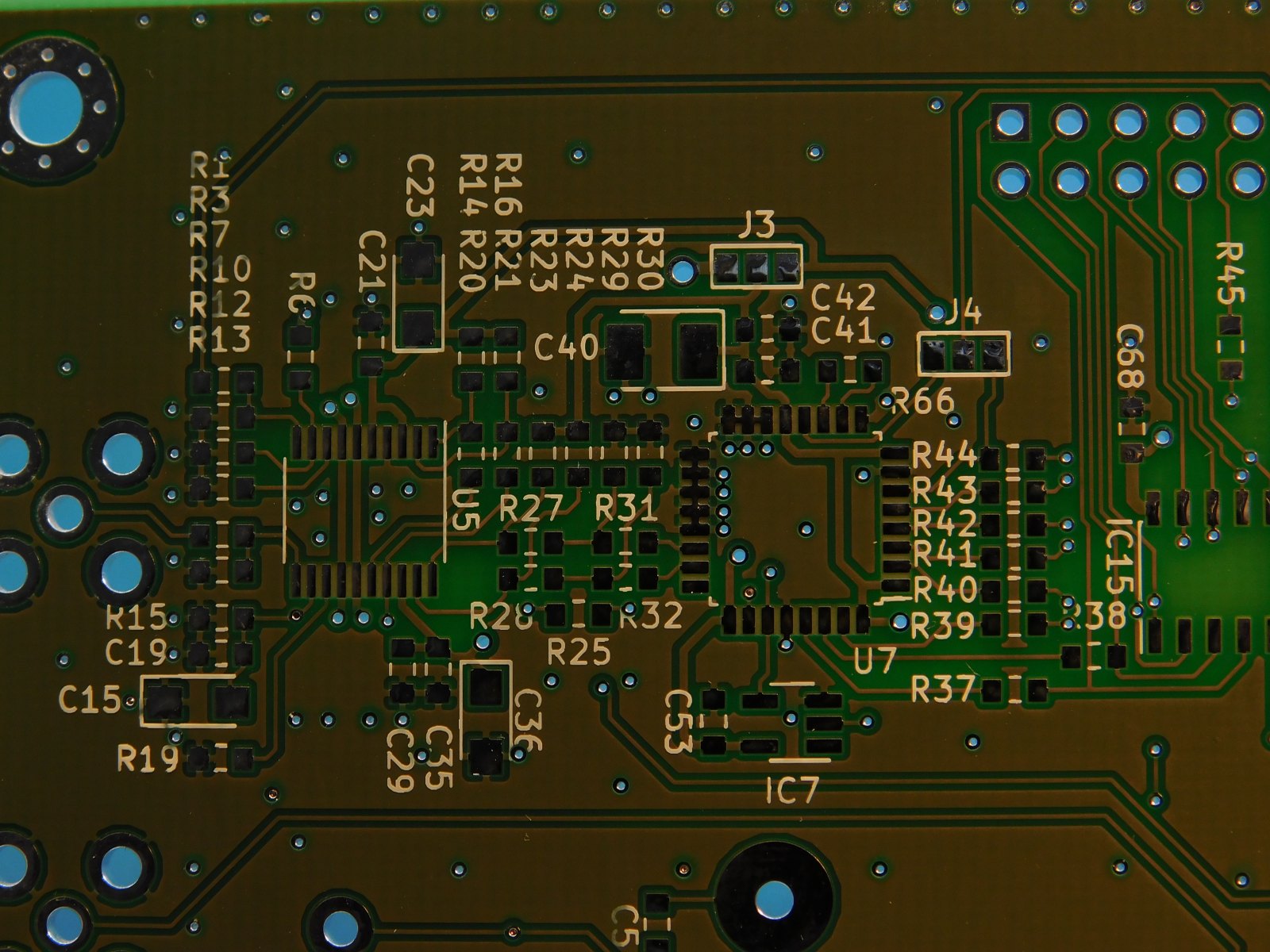

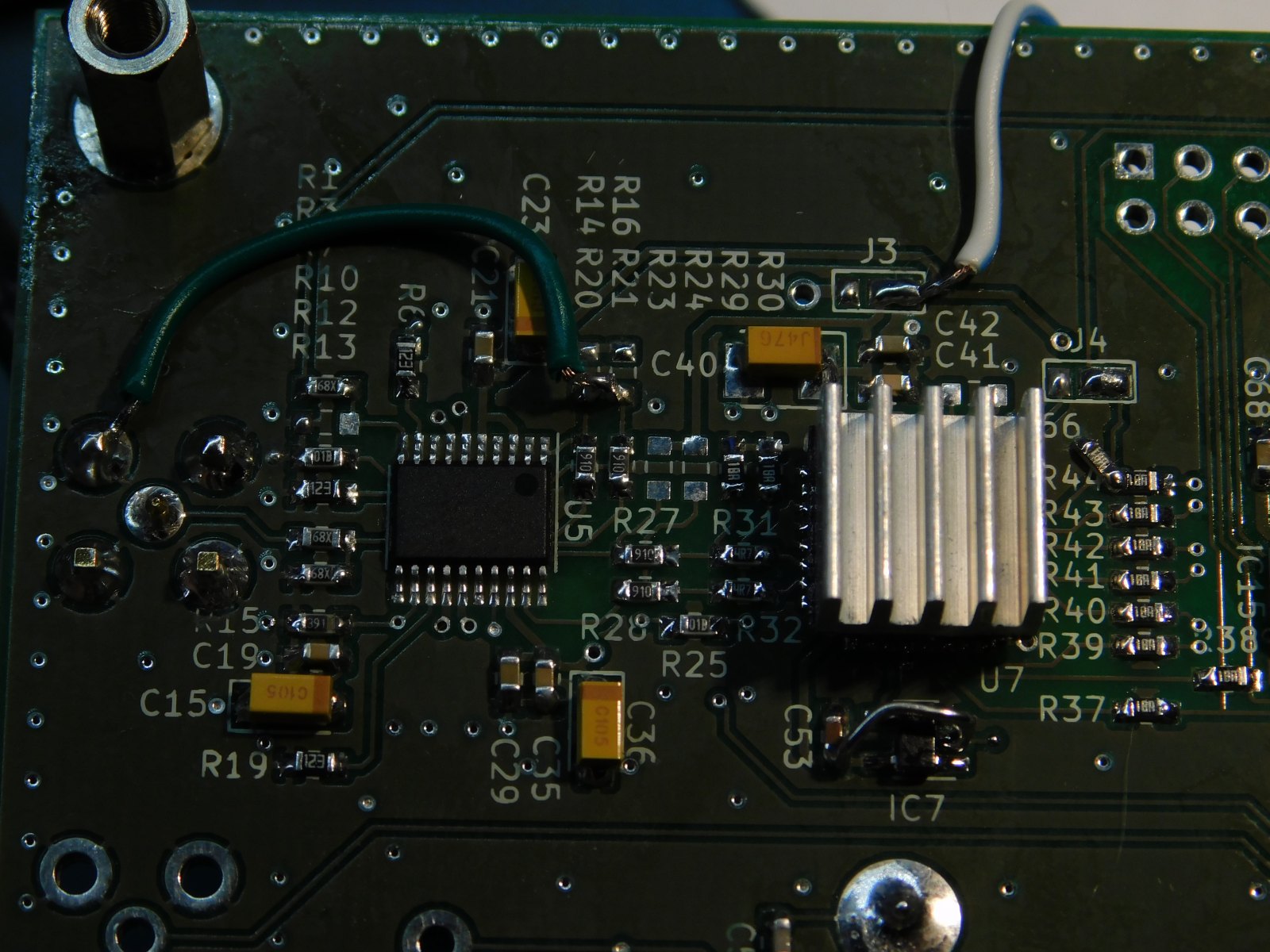

Dlouze, předlouze jsem hledal vhodný čítač na vstup. Nejrychlejší obvody řady 74VHC393 jdou “pouze” do 170MHz, pak už by bylo třeba použít děličku a zbytečně ztrácet rozlišení. Po několikatýdenním hledání vhodného obvodu jsem narazil na obvod MC100EP016A. To je synchonní čítač s ECL logikou pracující dle datasheet až do kouzelných 1,4GHz. V našem zapojení pracuje skutečně až do 1380MHz.

Potřebuje však diferenciální buzení, to by asi šlo nahradit jednoduchým buzením s umělou zemí na druhém dif. vstupu, ale riziko, že to vnese další možnou chybu, popřípadě nebude fungovat vůbec, jsme nechtěli podstupovat. Takže jsem musel najít vhodný budič na vstup, který potřebný diferenciální signál “Clock” vyrobí. Využil jsem velmi rychlý komparátor MAX 9601. Tento obvod dovede zpracovávat/generovat periodický signál s maximální frekvencí odpovídající 4Gbps, takže bychom měli využít celý rozsah vstupního čítače. Měřený signál X přivádíme na neinvertující vstup (pin 11) diff. OZ MAX9601. Na invertující vstup přivedeme ss napětí “Trigger” potřebné velikosti, toto napětí generujeme 12bit DA převodníkem v CPU.

Hystereze operačního zesilovače odpovídá rezistoru R19 (12k), ta je nastavitelná v intervalu 2-65mV (12k odpovídá hysterezi 20mV).

OZ má rozdělené napajení, symetrické Vcc/Vee pro vlastní OZ a Vcco pro napájení výstupních budičů. Budiče výstupů Q a /Q jsou v zapojení s otevřeným emitorem, takže potřebují pull-down resistory (R14+R16 a R29+R30).

V datasheet k MC100EP016A jsou nakreslené pull-up, což je chyba.

Co nejblíže pouzdra OZ jsou filtrační/blokovací kondenzátory. 1μF jako BULK a pak 100nF+1nF jako blokovací pro vykrývání krátkodobých proudových špiček.

Druhý operační zesilovač U5A zajišťuje dostatečné přesné/strmé spínání signálu GATE, po který čítač čítá. Výstupem Q (pin 1) spíná LE vstup operařníko zesilovače U5B a /CE vstup asynch. 8 bit čítače MC100EP016A.

Výstupem z čítače U7 je 8-mi bitový signál, kde bit D0 má nejnižší váhu (LSB) a vstupní signál CLK dělí dvěma. D7 má pak největší váhu (MSB) a dělí CLK 256-ti. To znamená, že při vstupním kmitočtu 1380MHz je na D7 kmitočet f/256, tedy cca 5,4MHz, což už spolehlivě zvládne klasická logika. Tou je 8-mi bitový čítač 74HC393D, jeho výstup již jde přímo do CPU, kde navazují čítače další. Celkem takto získáme binární čítač až do XXX bitů.

Jednotlivé výstupy z čítačů U7 a IC8 vedou do multiplexerů 74HC151 IC15+IC16. Takto můžeme přečíst bitový stav po skončení měření (GATE).

Časová základna

Srdcem časové základny je dvojitě vyhřívaný krystalový oscilátor (OCXO) Trimble 34310. Jeho výstup kmitá na 10MHz a pomocí ladícího pinu ho lze rozlaďovat o cca ± 2Hz, napěťová závislost je cca 1,5Hz/V. Těchto 10MHz natvarujeme v IC2. Poté ho vydělíme 10-ti pomocí IC4A(74HC390D) a takto získaný 1MHz signál spolu s 1MHz výstupem generovaným pomocí GPS přivedeme na vstupy XOR hradla. Takto můžeme srovnávat jejich fázi a velmi přesně “doladit” náš místní krystalový oscilátor. Tímto dokážeme využít krátkodobou přesnost GPS (Cesiové hodiny) a vynikající dlouhodobou přesnost OCXO Trimble oscilátoru. Celková přesnost 10MHz signálu časové základny může dosahovat stability až 2×10-12 Hz (0,002 PPB). 1MHz časové základny se v kaskádách dále dělí opět vždy 10ti. Takto získáme signály o kmitočtu 100Hz, 10Hz, 1Hz, 100mHz, 10mHz, 1mHz, ze kterých uděláme pulzy se střídou 1/10 pomocí NAND hradel (IC14 + IC19). Ty jsou vyvedeny do multiplexeru časové základny. Výstupní pulz je tedy v 90% času v log 1 (doba měření – GATE) a 10% času v log 0, kdy se přečtou a vynulují všechny čítače pomocí CPU. V další měřící periodě se pak vše opakuje.

Následující video ukazuje zavěšení PLL. Konkrétně ve studeném stavu OCXO, takže celá stabilizace trvá cca 30s, protože se nahřívá a tím pádem rozlaďuje krystal. Na displeji voltmetru jde vidět zesílené ladící napětí (na C6) z výstupu integračního článku R18+C24. To se mění v rozsahu 2-7,5V, kde osciluje v závislosti na střídě výstupu IC3B.

V nahřátém stavu trva zavěšení cca 2s, ladící napětí pak kolísá v intervalu cca 5mV. To odpovídá rozladění OCXO o cca 0,0075Hz ∼ 8mHz.

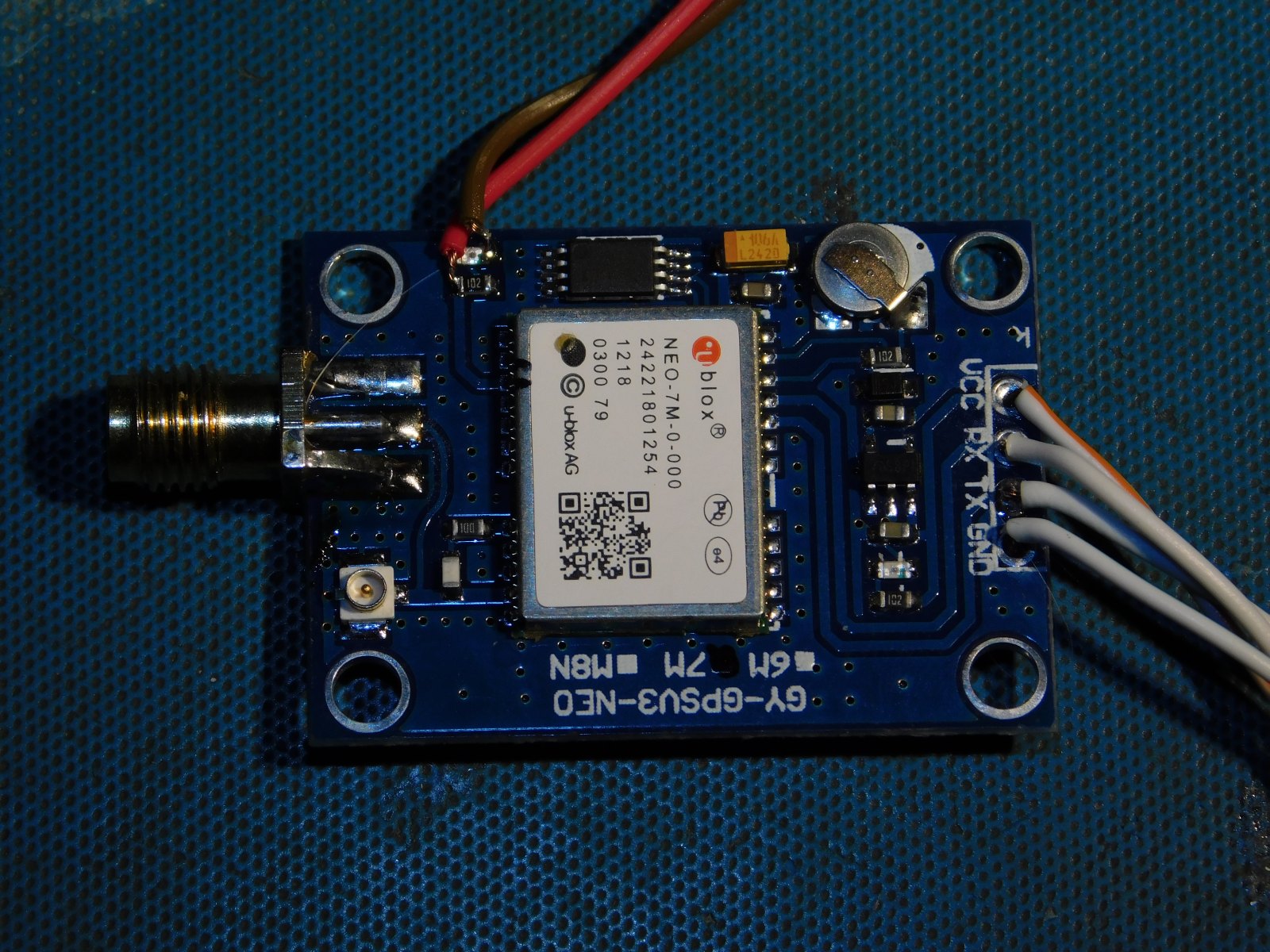

GPS Přijímač:

GPS přijímač slouží především ke generování přesného taktovacího signálu 1MHz, který bude synchronizovat OCXO časové základny. Dále z něj budeme prostřednictvím seriové linky vyčítat další potřebné informace jako je přesný čas, zeměpisnou polohu pro výpočet lokátoru, počet přijímaných satelitů a v případě spuštění přerušení i velmi přesnou časovou značku události.

Modul displeje, modul vstupního obvodu (transformace impedancí), programování a celkové HW zpracování budeme prezentovat v následujících článcích.